# A VLSI Architecture for Computing Scale Space\*

#### N. RANGANATHAN AND MUBARAK SHAH

Department of Computer Science, University of Central Florida, Orlando, Florida 32816

Received May 7, 1987; revised February 24, 1988

Meaningful information about a scene is captured in the intensity changes in an image. These intensity changes occur at various scales depending on their physical origins. Scale-space generated by applying the Laplacian of Gaussian edge detector to the image at a continuum of scales is a powerful representation for detecting and organizing these intensity changes symbolically and has proved to be very useful for one-dimensional signals. The high computational cost of generating scale-space in two dimensions has restricted its use in images. This paper proposes a very efficient single chip VLSI design for scale-space computation in one and two dimensions. The architecture of the chip is based on an algorithm that can provide speeds that are of an order of magnitude higher than the speeds obtainable from other systems proposed in the literature. The design uses the principles of modularity, expandability, and parallelism, and fully utilizes the three properties of Gaussian symmetry, separability, and scaling. Moreover, our proposed algorithm does not approximate the Laplacian of the Gaussian operator; it uses instead four one-dimensional convolutions to obtain the computations in two dimensions. The proposed architecture has not been built. © 1988 Academic Press.

CONTENTS. 1. Introduction. 1.1. Motivation. 1.2. Purpose. 1.3. Outline of paper. 2. Related Work. 3. Approach. 4. One Dimension. 4.1. VLSI architecture for the LG convolution. 4.2. PE architecture and operation. 4.3. Systolic version of the proposed architecture. 4.4. Normalization. 4.5. Zerocrossing detector. 5. Two Dimensions. 6. Chip Implementation Issues. 7. Conclusions. Appendix.

#### 1. INTRODUCTION

### 1.1. Motivation

The goal of computer vision is to build algorithms for recovering explicit and meaningful information about a scene from the images. This information is useful to recognize instances of real world objects. Information about the scene is captured in the intensity changes across time and space. The intensity changes in space signify the discontinuities due to boundaries of objects, depth, and surface orientation. The changes across the time axis, on the other hand, carry the information about the motion of objects and cues to occlusion. These intensity changes occur at various scales depending on the sizes and motion characteristics of objects. Sometimes, it is possible to find an instance of change at a particular scale, when it can not be found at other scales.

Marr [17] argued that attributes carrying the valuable information about the physical process—e.g., a regular patchwork of wheat, a stalk of wheat, and the grains on the stalk of wheat—may emerge at any range of scales in the real world

\*The research reported in this paper was supported in part by Center for Research in Electro Optics and Lasers (CREOL), University of Central Florida under Grant 20-52-043 and by the National Science Foundation under Grant IRI 87-13120.

and more so in images because of additional transformation introduced during the imaging process. In order to capture the useful information in an image, Marr and Hildreth [14] proposed the use of the Laplacian of the Gaussian (LG) edge detector. In their scheme, they convolve an image with a number of LG operators of different scales and detect zerocrossings in the result. They found that spatial coincidence of zero crossings at all scales may signal the presence of a physical edge.

Marr and Hildreth [14] used the LG operator at four different scales with Gaussians having standard deviations  $\sigma = 1, 2, 4, 8$ . This was motivated neurophysiologically because of the evidence of four bandpass channels found in the retina. Recently, Witkin [28] proposed the scale-space approach in which he used a continuum of scales. The scale-space representation is obtained by plotting the locations of zero crossings along the x-axis as a function of scale parameter  $\sigma$  in the x- $\sigma$  space. Witkin found that these zero crossings form contours like arches, and as one sweeps across the apex of an arch with increasing  $\sigma$ , the zero crossings disappear in pairs. By proposing the notion of scale-space, Witkin not only reaffirmed the importance and strength of scale-space representations, but he also intrigued many researchers, resulting in several papers: [32, 30, 26, 31, 1, 5, 15, 16, 6, 25, 23, 24, 22, 20].

## 1.2. Purpose

Several researchers have proposed hardware implementations of the LG operator, but none fully exploited the advanced VLSI technology and the properties of the Gaussian, namely scaling, separability, and symmetry. Therefore, no suitable architecture for the LG operator exists which can be extended for scale-space. The previous architectures have used off-the-shelf LSI components like multiplier chips which forced them to implement the system with several machine wire-wrapped boards [19]. In [11], a hardware system for the Gaussian convolution has been proposed. Each processor in the systolic array is implemented as a basic convolver board and the circuitry for each board is complex. Also, the need for a huge PLA to produce the complex control logic makes their architecture inefficient in space and time. In [2], the zero crossing detector is implemented using a PLA and the critical delay for the PLA determined the clock for the whole chip. Another approach proposed in [10] uses a processor per pixel, but it will work only when the mask size is 3 by 3 and the operator coefficients are powers of two. With the advanced VLSI technology [18] and experience available today, it is possible to integrate more hardware into a single chip and obtain faster and more cost efficient systems.

Previously, the researchers have limited the use of the powerful scale-space representation technique to only one dimension. The high computational cost of scale space in two dimensions has restricted its use in two-dimensional images. In fact, the first implemented version of the LG operator took about three hours to compute the zero crossings in the coarse channel of an image 512 pixels square, the smallest operator being roughly 35 picture elements [4]. The computation of

<sup>&</sup>lt;sup>1</sup>Laplacian of Gaussian is defined as  $\nabla^2 g(x, y) = (\partial^2/\partial x^2)g(x, y) + (\partial^2/\partial y^2)g(x, y)$ , where  $g = e^{-(x^2+y^2)/2\sigma^2}$  is a bivariate Gaussian filter. The standard deviation  $\sigma$  of the Gaussian is related to the scale parameter of the filter. The application of LG edge detector is equivalent to the convolution of an image with  $\nabla^2 g$ , i.e.,  $I \cdot \nabla^2 g$ .

scale-space requires even more time, because it involves the applications of LG at many scales.

The separability, symmetry, and scaling properties of Gaussian can be exploited in order to obtain an efficient implementation of scale-space in hardware. The purpose of this paper is to propose a special-purpose architecture that will use these properties of the Gaussian and the power of VLSI to the maximum extent in order to achieve high throughput as well as speed for the scale-space.

## 1.3. Outline of Paper

This paper proposes an efficient single chip VLSI design for scale-space computation in both one and two dimensions. The architecture of the chip is based on an algorithm that can provide speeds that are an order of magnitude higher than the speeds obtainable from other systems proposed in the literature [19]. The design uses the principles of modularity, expandability, and parallelism, and fully utilizes the three properties of Gaussian symmetry, separability, and scaling. In our approach, the entire convolver is implemented as a set of processing elements (PEs) working in parallel, with each PE organized as a pipeline. The circuit for the PE is simple with minimal control logic. The host broadcasts a new pixel value during each clock cycle, and after the pipe in the first PE is filled, the host receives back a result during each cycle. Each PE is a pipeline of several stages consisting of registers, adders, and a Wallace multiplier. The Wallace multiplier [27] itself consists of isolated adder stages. Thus, the clock for the chip is dependent entirely on the delay of an adder and we can obtain a fast implementation of our scheme. Our architecture is flexible and can be adapted to implement systems that use different mask sizes.

The organization of the rest of the paper is as follows. In the next section, we review the related work on the hardware implementation of the LG operator and identify the short comings of the proposed architectures. We will outline our approach in Section three. The hardware design for one-dimensional scale-space is presented in Section four, while the extension of this design to two dimensions is reported in Section five. Finally, the chip implementation issues and performance estimates are explored in Section six.

#### 2. RELATED WORK

Nishihara and Larson [19] built prototype hardware for implementing the LG operator which is based on the difference of Gaussian approximation. Their approach allows masks up to 32 by 32 in size. They have used separability to reduce the two-dimensional convolution into two one-dimensional convolutions. However, it appears that the symmetry and scaling properties were not used. They have used off-the-shelf components like the TRW multiplier chips. Also they mention the use of a hardware zero-crossing detector module, but do not give any design details. Their project goal was to gain the experience of building hardware for a vision system. They built a hardware system using machine wire-wrapped boards for the stereo matcher problem. It is possible to build more efficient and compact hardware systems by taking advantage of the VLSI technology.

An important point to be noted here is that Nishihara and Larson based their implementation on the difference of Gaussian approximation of the LG operator. Marr and Hildreth reported that the Laplacian of the Gaussian could be approxi-

mated by the difference of two Gaussians with standard deviation ratio of 1.6, but this was never formally justified [14]. Due to this, many researchers have used different ratios of standard deviations for this approximation. For instance, Crowley and Parker [7] used a ratio of 1.4 and Fleet et al. [9] used ratios of 1 and 2.5. Recently, it has been reported in the literature that the LG operator can also be approximated by a difference of offset Gaussians D.O.O.G. [29]. In this paper, however, we will not deal with an approximation. We will show that the LG can be computed without approximations using four one-dimensional convolutions. Our method has the same computational complexity as the ones that use approximations.

Batali [2] describes the implementation of a chip that computes the approximation to the two-dimensional gradient and detects zero crossings. The input to this chip is a raster-scanned digital stream of a two-dimensional video image that has already been convolved with the Laplacian of the Gaussian operator. The problem of gradient computation is beyond the scope of our paper. The chip uses a PLA implemented as a finite-state machine for detecting zero crossings. The author himself points out that the critical path in the AND plane of the PLA affects the clock for the whole chip. The design which we propose uses precharge logic and has a critical delay equal to that of an exclusive-OR stage, thus it is faster than that of Batali.

A VLSI-based systolic architecture for Gaussian convolution has been proposed by Giordano et al. in [11]. Their architecture uses a Booth's multiplier [3], ripple carry adder, and a microprogrammed ROM with complex control logic for the basic convolver board. The clock is dependent on the multiplier unit which was predicted as 125 ns. However, each basic convolver operation, a multiplication plus an addition, requires several cycles before the product is broadcast on the output bus. The choice of Booth's multiplier in such a situation where a large number of multiplications have to be performed is not good, since it may take anywhere from 16 to 24 cycles to perform one 8-bit multiplication. Moreover, the authors have not taken advantage of the symmetry and scaling properties of the Gaussian, which we will show simplifies the overall hardware significantly.

Georgiou and Anastassiou [10] have proposed a single chip architecture for the Laplacian operator which is suitable only for masks of size 3 by 3 and cannot be used for larger masks. In a 3 by 3 convolution, there is communication only to the eight nearest neighbors, whereas for larger masks, communication with PEs farther away is required. A PE organization with such capability would be complex and therefore, it is not economical to assign one PE per pixel. Furthermore, the paper assumes that the weights are powers of two in order to do multiplication by shift left. However, this assumption does not hold for all the operators, for example, the LG operator. There are two important points to be noted here. First, in general, masks of much larger size, as in the Gaussian filter, are desirable. Second, the weights in most operators are not powers of two. The first factor raises the need for VLSI architectures that are general enough for application to larger masks. The second factor dictates the use of a hardware multiplier within each PE. If each PE needs to have a hardware multiplier, then the concept of a PE per pixel is ruled out since it is extremely expensive in terms of hardware. Thus, we need an architecture that will exploit the power of VLSI and at the same time will be suitable for convolution of any size window.

#### 3. APPROACH

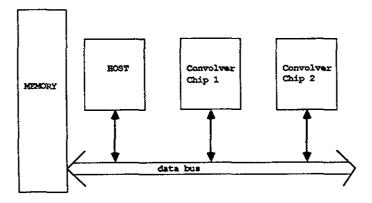

Our design is based on the principles of modularity, expandability, and parallelism. The system architecture should be modular in nature, so that each module of the system can be treated separately from the rest in terms of its input, output and the function. Our system has three main modules, the convolver, the normalizer, and the zero-crossing detector. The convolver, in turn, is a set of processing elements (PEs), where each PE has four submodules: FIFO buffers, two adders, and a multiplier. With a modular system it is easier to obtain different functions by doing simple changes to the system. The design we propose in this paper, can be used to compute the Gaussian filter, the Laplacian of the Gaussian edge detector, and scale-space.

Expandability is a very important feature in hardware systems; that gives the flexibility to expand the basic design to solve problems of similar nature, but of larger dimensions. The basic design in our approach for one dimension can be easily expanded for computations of higher dimensions. We will discuss in Section 5 how the hardware for one-dimensional convolution can be used to compute two-dimensional convolution and scale space. Finally, the purpose of our proposed architecture is to design a highly parallel real-time hardware. In our architecture, each PE is organized as a pipeline of 8 + m stages, where m is the size of the mask and a total of 1 + (m/2) PEs are used. For instance, in the example discussed in the next section, m is equal to 5, and hence each PE consists of 13 stages and three such PEs are required by our algorithm. The pipeline architecture makes it possible for our algorithm to run in linear time (O(n + m)), where n is the number of pixels and m is the size of the mask. The host broadcasts one pixel value per clock cycle to the convolver chip. It takes 8 + m clock cycles to fill the pipe in the first PE, after which the host starts receiving the resultant pixel values at the rate of one per clock cycle. Thus, it takes n + 8 + m - 1 cycles to perform one-dimensional convolution with a mask of size m on n pixels. The relationship between the mask size m and  $\sigma$ depends upon many factors including the number of bits used in a particular implementation and has been discussed extensively in [13, 12]. Approximately, the value of the Gaussian  $e^{-x^2/2\sigma^2}$  becomes almost zero for  $x > |3\sigma|$ . Therefore, we suggest using  $m = 7\sigma$  for odd values of  $\sigma$  and  $m = 7\sigma + 1$  when  $\sigma$  is even.

Besides the above three principles, our implementation fully utilizes the three properties of the Gaussian, i.e., scaling, symmetry, and separability. When convolved with itself, the Gaussian of standard deviation  $\sigma$ , yields a larger Gaussian of standard deviation  $\sqrt{2}\sigma$ . That is, if an image has been filtered with a Gaussian at a certain spread  $\sigma$  and if the same image must be filtered with a larger Gaussian with spread  $\sqrt{2}\sigma$ , then, instead of filtering the image with the larger Gaussian, the previous result can just be filtered with the same filter of spread  $\sigma$  used to obtain the desired image. Thus, the total number of operations for filtering the image by Gaussian of  $\sigma$  and  $\sqrt{2}\sigma$  will be equal to  $2n\sigma$ . The above process is called scaling. However, without scaling, the number of operations will be approximately equal to  $2.4n\sigma$ . This produces a significant reduction in the number of operations needed for computations like generating scale-space, where operators of multiple sizes are applied to the same image.

The scaling property of the Gaussian also holds in two dimensions. Although, the second derivative of the Gaussian in one dimension and the Laplacian of Gaussian in two dimensions do not possess this scaling property, it is possible to obtain the

effect of applying bigger operators by repeatedly applying the smaller operators to the image. First apply the second derivative of the Gaussian operator of size  $\sigma$  to the image and then apply the Gaussian of size  $\sigma$  to the output. The result will be equivalent to the output obtained by applying the second derivative of the Gaussian operator of size  $\sqrt{2}\sigma$ . In the Appendix, we state and prove a proposition for the general case.

Our approach is to design an architecture that can be used for convolutions of windows of any size. Once the chip is built for a particular mask size, say 7, it can be used as shown in the above paragraph for masks of any bigger size. For masks of smaller size, we need to turn "OFF" the unneeded PEs and use smaller size FIFO buffers. This can be done easily by replacing the FIFOs in our design with variable size FIFOs.

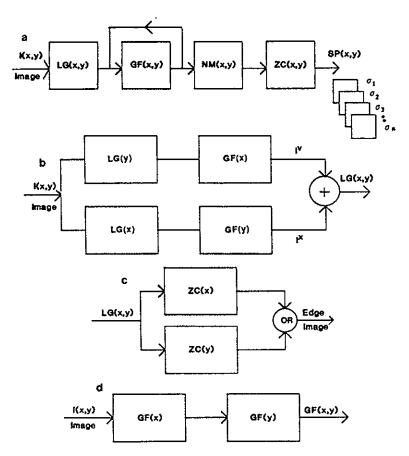

A two-dimensional Gaussian filter can be separated into two one-dimensional Gaussians, one along the x direction and the other along the y direction. Therefore, the Gaussian filter can be applied to an image by convolving first with a one-dimensional Gaussian along each row and then convolving the result again with a one-dimensional Gaussian along each column. Each one-dimensional convolution with an operator of size m requires m multiplications per pixel. Hence, two one-dimensional convolutions require 2m multiplications, which is a significant improvement over the  $m^2$  multiplications needed for a two-dimensional convolution. Unfortunately, the LG operator is not separable into two single-dimensional operators which is due to the fact that the Laplacian is not separable, even though the Gaussian is. We give an algorithm to decompose the two-dimensional LG convolution into four one-dimensional convolutions. This scheme requires 4m multiplications. For a large m, 4m multiplications are less than  $m^2$  multiplications. Therefore, the number of multiplications is significantly reduced for larger images. This will also be shown in the Appendix. We can summarize the algorithm for the decomposition of the operator as follows, refer to Fig. 9b for details:

- (1) Convolve the image with a second derivative of Gaussian mask along each row.

- (2) Convolve the resultant image from step (1) by a Gaussian mask along each column. Call the resultant image  $I^x$ .

- (3) Convolve the original image with a second derivative of Gaussian mask along each column.

- (4) Convolve the resultant image from step (3) by a Gaussian mask along each row. Call the resultant image  $I^{\nu}$ .

- (5) Add  $I^x$  and  $I^y$ .

The Gaussian is symmetric around the origin, i.e., g(x) = g(-x) for any x. This property can be used to reduce the number of multiplications as follows. Assume that the operator of size 5 is to be applied to the input sequence  $X_1, X_2, X_3, X_4, X_5, X_6, \ldots, X_n$  in order to get the output sequence  $Y_4, Y_5, Y_6, \ldots$ . For instance, the equation for the computation of  $Y_5$  is

$$Y_5 = w_0 X_1 + w_1 X_2 + w_2 X_3 + w_3 X_4 + w_4 X_5.$$

Due to the symmetry,  $w_0 = w_4$  and  $w_1 = w_3$ . The convolution equations can be

$$Y_{4} = w_{0}X_{4} + w_{1}(X_{3} + X_{1}) + w_{2}X_{2}$$

$$Y_{5} = w_{0}(X_{5} + X_{1}) + w_{1}(X_{4} + X_{2}) + w_{2}X_{3}$$

$$Y_{6} = w_{0}(X_{6} + X_{2}) + w_{1}(X_{5} + X_{3}) + w_{2}X_{4}$$

$$Y_{7} = w_{0}(X_{7} + X_{3}) + w_{1}(X_{6} + X_{4}) + w_{2}X_{5}$$

$$Y_{8} = w_{0}(X_{8} + X_{4}) + w_{1}(X_{7} + X_{5}) + w_{2}X_{6}$$

$$Y_{9} = w_{0}(X_{9} + X_{5}) + w_{1}(X_{8} + X_{6}) + w_{2}X_{7}$$

$$Y_{10} = w_{0}(X_{10} + X_{6}) + w_{1}(X_{9} + X_{7}) + w_{2}X_{8}$$

$$Y_{11} = w_{0}(X_{11} + X_{7}) + w_{1}(X_{10} + X_{8}) + w_{2}X_{9}$$

$$Y_{12} = w_{0}(X_{12} + X_{8}) + w_{1}(X_{11} + X_{9}) + w_{2}X_{10}$$

....

Fig. 1. The equations for LG convolution for mask size = 5.

simplified as shown in Fig. 1. Utilizing symmetry, we reduce the number of multiplications to compute all the  $Y_i$  elements, from 5n to 3n, where n is the total number of elements. In general, when using the property of symmetry, we only have to perform (m/2 + 1) \* n multiplications which is a significant reduction from m \* n, where m is the number of weights in the mask.

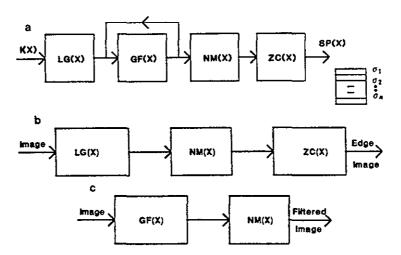

#### 4. ONE DIMENSION

In this section, we will present the hardware design for computing the scale-space in one dimension and the design will be extended to two dimensions in the next section. The different stages in computing one-dimensional scale-space are shown in Fig. 2a. They are four main stages: Laplacian of the Gaussian LG(x), Gaussian filter GF(x), normalization NM(x), and zero-crossing detector ZC(x). Also, we can obtain a one-dimensional edge detector and a Gaussian filter with stages as depicted in Figs. 2b,c. The one-dimensional edge detector is realized by applying the Laplacian of the Gaussian operator to the image, normalizing the resultant pixel values, and then applying the zero-crossing detector. The Gaussian filter is obtained by convolving the image with the Gaussian and normalizing the resultant pixel values.

### 4.1. VLSI Architecture for the LG Convolution

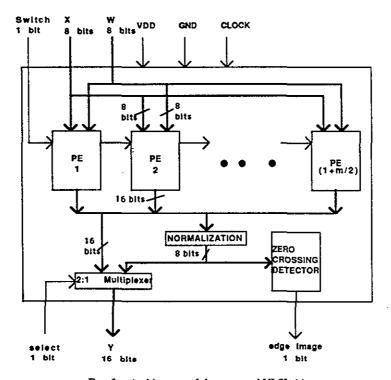

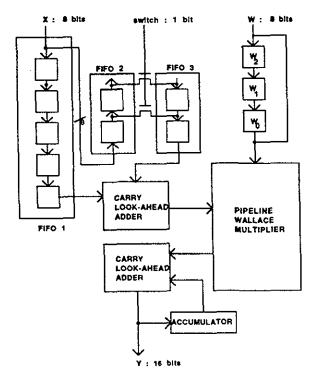

The VLSI architecture for the computation of the Gaussian and the LG convolutions is given in Fig. 3. The architecture consists of a certain number of PEs organized in parallel with a common input and output bus as shown in the figure. A zero-crossing detector module is also included which will output the binary image. In a binary image, a "1" represents the presence of a zero crossing, while a "0" represents the absence. The chip needs a total of 38 pins. Eight of the input pins are for the pixel data, eight for the weights, one pin for the switch bit needed by the PEs, one for multiplexing the output, and three for VDD, GND, and CLOCK. There is one output pin for the edge image and 16 pins for the convolved image. The 16-bit pixel values obtained from the convolution are normalized to 8-bit results by the normalization module and then input to the zero-crossing detector circuit. The design of the normalization module is discussed later in Subsection 4.4. The 2:1 Multiplexer selects between the 16-bit pixel values and the normalized 8-bit results.

FIG. 2.(a). One-dimensional scale-space. The image I(x) is convolved with the Laplacian of the Gaussian LG(x) and then convolved with Gaussian GF(x) repeatedly depending on the scale needed. The resultant pixel values are normalized in the next stage NM(x) and in the final stage ZC(x), the zero crossings are detected to produce the edge image. SP(x) is the scale-space generated at various scales. (b) One-dimensional edge detector. The one-dimensional edge detector is realized by applying the Laplacian of Gaussian operator LG(x) to the image I(x), normalizing the resultant pixel values (shown as NM(x) stage), and then applying the zero-crossing detector ZC(x). (c) One-dimensional Gaussian filter. The Gaussian filter is realized by convolving with the Gaussian, shown as GF(x), and normalizing the resultant pixel values (shown as NM(x) stage).

FIG. 3. Architecture of the proposed VLSI chip.

When the normalized results are selected, the most significant 8 bits of the output (Y) will provide the normalized result and the other 8 bits shall be ignored. The required output can be obtained by setting the select pin appropriately. The number of processing elements (PEs) will be equal to 1 + m/2, where m is the size of the mask as well as the number of weights required for the convolution.

The parallel algorithm for one-dimensional LG convolution will be explained with the help of an example where the size of the mask is 5, and therefore the number of PEs is 3. The equations for this example are given in Fig. 1. The image pixel values, called  $X_i$ , are broadcast to all the PEs at once. The host sends a new  $X_i$  to the chip during each cycle and when the pipe within the PE is filled, each PE starts producing a  $Y_i$  element every third cycle, which is relayed on the output bus. In general, a PE will produce  $Y_i$  values with a gap of cycles equal to  $\lfloor m/2 \rfloor$  which is one less than the number of PEs and hence the output bus is time-shared by the PEs. Thus, a resultant  $Y_i$  value is produced at the rate of one per clock cycle. In our example, first, PE1 computes  $Y_4$ ; during the next cycle PE2 computes  $Y_5$ ; and then PE3 follows with  $Y_6$  during the third. After this, PE1 is ready again with  $Y_7$  and so on. We will demonstrate how we can obtain this synchronization by suitably designing the PE architecture.

TABLE 1a

Trace of Clock-Step Execution of PEI for the Architecture of Fig. 3

| Inhuc                  |                                                                                                                                                                                                         | 161                                                                                                                                                                                                                                               | EO. 1                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                       | DIE.                                                  | 0.2                                                   |                                                       |                                                       |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|

|                        | 1                                                                                                                                                                                                       |                                                                                                                                                                                                                                                   | 3                                                                                                                                                                                                                                                                                                                                                            | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5                                                     | 6                                                     |                                                       | CLA-1                                                 | Start<br>multiply                                     |

| X <sub>1</sub>         | X <sub>1</sub>                                                                                                                                                                                          | ø                                                                                                                                                                                                                                                 | ø                                                                                                                                                                                                                                                                                                                                                            | ø                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ø                                                     | ø                                                     | ø                                                     | <del>-</del>                                          |                                                       |

| <i>X</i> <sub>2</sub>  | <i>X</i> <sub>2</sub>                                                                                                                                                                                   | <i>X</i> <sub>1</sub>                                                                                                                                                                                                                             | Ø                                                                                                                                                                                                                                                                                                                                                            | Ø                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ø                                                     | ø                                                     | ø                                                     |                                                       |                                                       |

| <i>X</i> <sub>3</sub>  | <i>X</i> <sub>3</sub>                                                                                                                                                                                   | <i>X</i> <sub>2</sub>                                                                                                                                                                                                                             | <i>X</i> <sub>1</sub>                                                                                                                                                                                                                                                                                                                                        | Ø                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ø                                                     | ø                                                     | ø                                                     | _                                                     | <del>-</del>                                          |

| X <sub>4</sub>         | <i>X</i> <sub>4</sub>                                                                                                                                                                                   | <i>X</i> <sub>3</sub>                                                                                                                                                                                                                             | <i>X</i> <sub>2</sub>                                                                                                                                                                                                                                                                                                                                        | X <sub>1</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ø                                                     | X <sub>3</sub>                                        | <i>X</i> <sub>4</sub>                                 | _                                                     | -                                                     |

| <i>X</i> <sub>5</sub>  | X <sub>s</sub>                                                                                                                                                                                          | X <sub>4</sub>                                                                                                                                                                                                                                    | <i>X</i> <sub>3</sub>                                                                                                                                                                                                                                                                                                                                        | <i>X</i> <sub>2</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <i>X</i> <sub>1</sub>                                 | ø                                                     | <i>X</i> <sub>3</sub>                                 | $\emptyset + X_4$                                     | <del>-</del>                                          |

| X <sub>6</sub>         | <i>X</i> <sub>6</sub>                                                                                                                                                                                   | <i>X</i> <sub>5</sub>                                                                                                                                                                                                                             | X <sub>4</sub>                                                                                                                                                                                                                                                                                                                                               | <i>X</i> <sub>3</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <i>X</i> <sub>2</sub>                                 | ø                                                     | Ø                                                     | $X_1 + X_3$                                           | $W_0(X_4)$                                            |

| X <sub>7</sub>         | <i>X</i> <sub>7</sub>                                                                                                                                                                                   | <i>X</i> <sub>6</sub>                                                                                                                                                                                                                             | <i>X</i> <sub>5</sub>                                                                                                                                                                                                                                                                                                                                        | X <sub>4</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <i>X</i> <sub>3</sub>                                 | <i>X</i> <sub>6</sub>                                 | <i>X</i> <sub>7</sub>                                 | $X_2 + \emptyset$                                     | $W_1(X_1+X_3)$                                        |

| X <sub>8</sub>         | <i>X</i> <sub>8</sub>                                                                                                                                                                                   | <i>X</i> <sub>7</sub>                                                                                                                                                                                                                             | <i>X</i> <sub>6</sub>                                                                                                                                                                                                                                                                                                                                        | <i>X</i> <sub>5</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <i>X</i> <sub>4</sub>                                 | ø                                                     | <i>X</i> <sub>6</sub>                                 | $X_3 + X_7$                                           | $W_2(X_2)$                                            |

| Х,                     | <i>X</i> <sub>9</sub>                                                                                                                                                                                   | X <sub>E</sub>                                                                                                                                                                                                                                    | <i>X</i> <sub>7</sub>                                                                                                                                                                                                                                                                                                                                        | X <sub>6</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                | X <sub>5</sub>                                        | ø                                                     | Ø                                                     | $X_4 + X_6$                                           | $W_0(X_3+X_7)$                                        |

| X <sub>10</sub>        | <i>X</i> <sub>10</sub>                                                                                                                                                                                  | <i>X</i> ,                                                                                                                                                                                                                                        | <i>X</i> <sub>8</sub>                                                                                                                                                                                                                                                                                                                                        | Χ <sub>γ</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <i>X</i> <sub>6</sub>                                 | <i>X</i> <sub>9</sub>                                 | X <sub>10</sub>                                       | $X_5 + \emptyset$                                     | $W_1(X_4+X_6)$                                        |

| <i>X</i> <sub>11</sub> | <i>X</i> <sub>11</sub>                                                                                                                                                                                  | X <sub>10</sub>                                                                                                                                                                                                                                   | <i>X</i> <sub>9</sub>                                                                                                                                                                                                                                                                                                                                        | <i>X</i> <sub>8</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <i>X</i> <sub>7</sub>                                 | ø                                                     | <i>X</i> <sub>9</sub>                                 | $X_6 + X_{10}$                                        | $W_2(X_5)$                                            |

| X <sub>12</sub>        | X <sub>12</sub>                                                                                                                                                                                         | <i>X</i> <sub>11</sub>                                                                                                                                                                                                                            | X <sub>10</sub>                                                                                                                                                                                                                                                                                                                                              | <i>X</i> <sub>9</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                         | X <sub>8</sub>                                        | ø                                                     | ø                                                     | $X_7 + X_9$                                           | $W_0(X_6+X_{10})$                                     |

| X <sub>13</sub>        | <i>X</i> <sub>13</sub>                                                                                                                                                                                  | X12                                                                                                                                                                                                                                               | <i>X</i> <sub>11</sub>                                                                                                                                                                                                                                                                                                                                       | <i>X</i> <sub>10</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Х,                                                    | X <sub>12</sub>                                       | X <sub>13</sub>                                       | <i>X</i> <sub>8</sub> + Ø                             | $W_1(X_7+X_9)$                                        |

| X <sub>14</sub>        | X <sub>14</sub>                                                                                                                                                                                         | X <sub>13</sub>                                                                                                                                                                                                                                   | X <sub>12</sub>                                                                                                                                                                                                                                                                                                                                              | <i>X</i> <sub>11</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                        | X <sub>10</sub>                                       | ø                                                     | X <sub>12</sub>                                       | $X_9 + X_{13}$                                        | $W_2(X_8)$                                            |

| X <sub>15</sub>        | X <sub>15</sub>                                                                                                                                                                                         | X <sub>14</sub>                                                                                                                                                                                                                                   | X <sub>13</sub>                                                                                                                                                                                                                                                                                                                                              | X <sub>12</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                               | X <sub>11</sub>                                       | Ø                                                     | ø                                                     | $X_{10} + X_{12}$                                     | $W_0(X_9 + X_{13})$                                   |

|                        | X <sub>2</sub> X <sub>3</sub> X <sub>4</sub> X <sub>5</sub> X <sub>6</sub> X <sub>7</sub> X <sub>8</sub> X <sub>9</sub> X <sub>10</sub> X <sub>11</sub> X <sub>12</sub> X <sub>13</sub> X <sub>14</sub> | X     1       X1     X1       X2     X2       X3     X3       X4     X4       X5     X5       X6     X6       X7     X7       X8     X8       X9     X9       X10     X10       X11     X11       X12     X12       X13     X13       X14     X14 | X     1     2       X1     X1     Ø       X2     X2     X1       X3     X3     X2       X4     X4     X3       X5     X5     X4       X6     X6     X5       X7     X7     X6       X8     X8     X7       X9     X9     X8       X10     X10     X9       X11     X11     X10       X12     X12     X11       X13     X13     X12       X14     X14     X13 | X     1     2     3       X1     X1     Ø     Ø       X2     X2     X1     Ø       X3     X3     X2     X1       X4     X4     X3     X2       X5     X5     X4     X3       X6     X6     X5     X4       X7     X7     X6     X5       X8     X8     X7     X6       X9     X9     X8     X7       X10     X10     X9     X8       X11     X11     X10     X9       X12     X12     X11     X10       X13     X13     X12     X11       X14     X14     X14     X13     X12 | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ |

### 4.2. PE Architecture and Operation

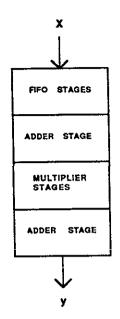

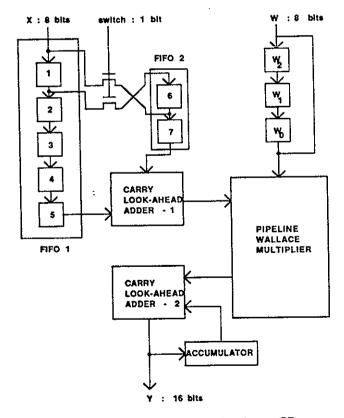

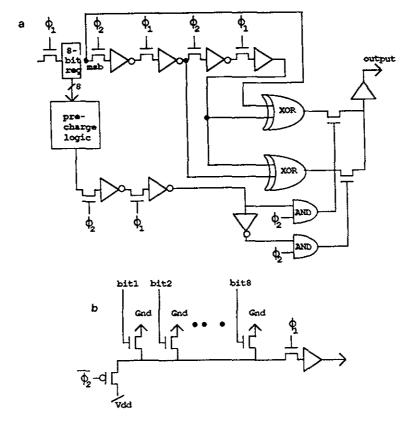

The PE is organized as a pipeline of several stages as shown in Fig. 4. This is essential in order to get high throughput and speed while convolving image data of the order of 1000 by 1000 pixels. The hardware organization of a processing element is given in Fig. 5. Each processing element consists of a pipeline Wallace multiplier, two carry look-ahead adders, an accumulator, a circular FIFO buffer for the weights, and two FIFO buffers for the incoming X, values. The weights are pre-loaded into the circular FIFO buffer before the computation starts. The  $X_i$ values enter the FIFO-1 at the rate of one every clock cycle. In order to use the symmetry property of the Gaussian,  $\lfloor m/2 \rfloor$  of the  $X_i$  values are needed in the reverse order. This is done by setting the control signal "switch" high during every third clock cycle (once the computation starts), for our example. The "switch" is connected to the gates of a set of enhancement mode n-channel MOSFET transistors [18] as shown in Fig. 5. The MOSFET transistors act as pass transistors that help to copy the data from FIFO-1 to FIFO-2. When the control signal "switch" is high, the pass transistors act as closed circuits allowing the data to pass through and when the control signal is low, the pass transistors act as open circuits and no data can pass through. The FIFO-1 buffer consists of five 8-bit registers organized in a

TABLE 1b

| Clock<br>cycle | CLA-2 addition                                             | Outbus<br>Y     |

|----------------|------------------------------------------------------------|-----------------|

| 8              | _                                                          |                 |

| 9              | _                                                          | _               |

| 10             |                                                            |                 |

| 11             | $W_0X_4 + (\emptyset)$                                     | _               |

| 12             | $W_1(X_1 + X_3) + (W_0X_4)$                                | _               |

| 13             | $W_2X_2 + (W_1(X_1 + X_3) + W_0X_4)$                       | _               |

| 14             | $W_0(X_3+X_7)+(\emptyset)$                                 | Y <sub>4</sub>  |

| 15             | $W_1(X_4 + X_5) + (W_0(X_3 + X_7))$                        | _               |

| 16             | $W_2X_5 + (W_1(X_4 + X_6) + W_0(X_3 + X_7))$               | _               |

| 17             | $W_0(X_6+X_{10})+(\varnothing)$                            | Y <sub>7</sub>  |

| 18             | $W_1(X_7 + X_9) + (W_0(X_6 + X_{10}))$                     |                 |

| 19             | $W_2(X_8) + (W_1(X_7 + X_9) + W_0(X_6 + X_{10}))$          |                 |

| 20             | $W_0(X_9 + X_{13}) + (\emptyset)$                          | Y <sub>10</sub> |

| 21             | $W_1(X_{10} + X_{12}) + (W_0(X_9 + X_{13}))$               |                 |

| 22             | $W_2(X_{11}) + (W_1(X_{10} + X_{12}) + W_0(X_9 + X_{13}))$ |                 |

FIG. 4. The pipeline stages in a PE.

Fig. 5. Architecture of a processing element (PE).

first-in first-out fashion and the FIFO-2 buffer consists of two 8-bit registers with additional load capability as shown in Fig. 5.

The 8-bit multiplier will have a five-stage pipeline where the first stage is the partial product generator and the second through fourth stages consist of carry save adders and the last stage is a 16-bit carry look-ahead adder [27]. As can be seen from the equations of Fig. 1, the same weight needs to be multiplied with two different pixel values. During each clock cycle, a new pair of pixel values are added in the carry look-ahead adder. The sum is input to the Wallace multiplier during the following clock cycle along with the weight to multiply it with. The weights are stored in a circular FIFO buffer. The weight input to the multiplier from the buffer is also loaded back into the buffer in a circular fashion, while the rest of the weights shift to the next stage nearer the multiplier. A new multiplication is initiated during each clock cycle. As the pixels are shifted into the carry look-ahead adder from FIFO-2, zeros are inserted in the other end. Thus, a zero is output by FIFO-2 during those cycles when no actual addition is required, which corresponds to the situation when a weight has to be multiplied with only one pixel in an equation. The outputs of the multiplier are summed up and stored in the accumulator in order to obtain the Y, value which is to be relayed on the output bus. A sample trace of the execution of the three PEs is given in the Tables 1-3. These tables illustrate the

TABLE 2a

Trace of Clock-Step Execution of PE2 for the architecture of Fig. 3

| Clock | Inbus                 |                        | F                      | IFO-1                  |                       |                       | FIF             | O-2                    |                     | Start               |

|-------|-----------------------|------------------------|------------------------|------------------------|-----------------------|-----------------------|-----------------|------------------------|---------------------|---------------------|

| cycle | X                     | 1                      | 2                      | 3                      | 4                     | 5                     | 6               | 7                      | CLA-1               | multiply            |

| 1     | <i>X</i> <sub>1</sub> | <i>X</i> <sub>1</sub>  | Ø                      | ø                      | Ø                     | ø                     | ø               | ø                      |                     |                     |

| 2     | X <sub>2</sub>        | <i>X</i> <sub>2</sub>  | X <sub>1</sub>         | Ø                      | ø                     | ø.                    | Ø               | Ø                      |                     |                     |

| 3     | <i>X</i> <sub>3</sub> | <i>X</i> <sub>3</sub>  | <i>X</i> <sub>2</sub>  | <i>X</i> <sub>1</sub>  | ø                     | Ø                     | ø               | Ø                      |                     | <del>-</del>        |

| 4     | <i>X</i> <sub>4</sub> | <i>X</i> <sub>4</sub>  | <i>X</i> <sub>3</sub>  | X <sub>2</sub>         | <i>X</i> <sub>1</sub> | ø                     | ø               | Ø                      |                     |                     |

| 5     | X <sub>5</sub>        | <i>X</i> <sub>5</sub>  | <i>X</i> <sub>4</sub>  | <i>X</i> <sub>3</sub>  | <i>X</i> <sub>2</sub> | <i>X</i> <sub>1</sub> | X <sub>4</sub>  | <i>X</i> <sub>5</sub>  |                     |                     |

| 6     | <i>X</i> <sub>6</sub> | <i>X</i> <sub>6</sub>  | X <sub>5</sub>         | X <sub>4</sub>         | <b>X</b> <sub>3</sub> | <i>X</i> <sub>2</sub> | ø               | X <sub>4</sub>         | $X_1 + X_5$         | _                   |

| 7     | X <sub>7</sub>        | Х,                     | <i>X</i> <sub>6</sub>  | <i>X</i> <sub>5</sub>  | <i>X</i> <sub>4</sub> | <i>X</i> <sub>3</sub> | ø               | ø                      | $X_2 + X_4$         | $W_0(X_1+X_5)$      |

| 8     | <i>X</i> <sub>8</sub> | X <sub>8</sub>         | X,                     | <i>X</i> <sub>6</sub>  | <i>X</i> <sub>5</sub> | <i>X</i> <sub>4</sub> | X <sub>7</sub>  | X <sub>8</sub>         | $X_3 + \emptyset$   | $W_1(X_2+X_4)$      |

| 9     | Х,                    | <i>X</i> <sub>9</sub>  | X <sub>8</sub>         | X <sub>7</sub>         | <i>X</i> <sub>6</sub> | <i>X</i> <sub>5</sub> | ø               | X7                     | $X_4 + X_8$         | $W_2(X_3)$          |

| 10    | X <sub>10</sub>       | <i>X</i> <sub>10</sub> | <i>X</i> <sub>9</sub>  | <i>X</i> <sub>8</sub>  | <i>X</i> <sub>7</sub> | <i>X</i> <sub>6</sub> | ø               | ø                      | $X_5 + X_7$         | $W_0(X_4+X_8)$      |

| 11    | X <sub>11</sub>       | <i>X</i> <sub>11</sub> | X <sub>10</sub>        | X <sub>9</sub>         | <i>X</i> <sub>8</sub> | Χ <sub>γ</sub>        | X <sub>10</sub> | <i>X</i> <sub>11</sub> | $X_6 + \varnothing$ | $W_1(X_5+X_7)$      |

| 12    | X <sub>12</sub>       | X <sub>12</sub>        | <i>X</i> <sub>11</sub> | <i>X</i> <sub>10</sub> | <i>X</i> <sub>9</sub> | <i>X</i> <sub>8</sub> | ø               | X <sub>10</sub>        | $X_7 + X_{11}$      | $W_2(X_6)$          |

| 13    | X <sub>13</sub>       | X <sub>13</sub>        | X <sub>12</sub>        | X11                    | X10                   | <i>X</i> <sub>9</sub> | ø               | Ø                      | $X_8 + X_{10}$      | $W_0(X_7 + X_{11})$ |

| 14    | X <sub>14</sub>       | X <sub>14</sub>        | X <sub>13</sub>        | <i>X</i> <sub>12</sub> | X <sub>11</sub>       | X <sub>10</sub>       | X <sub>13</sub> | X <sub>14</sub>        | $X_9 + \varnothing$ | $W_1(X_8 + X_{10})$ |

| 15    | X <sub>15</sub>       | X <sub>15</sub>        | X <sub>14</sub>        | X <sub>13</sub>        | X <sub>12</sub>       | X <sub>11</sub>       | Ø               | X <sub>13</sub>        | $X_{10} + X_{14}$   | $W_2(X_9)$          |

|       |                       |                        |                        |                        |                       |                       |                 |                        |                     |                     |

TABLE 2b

| Clock<br>cycle | CLA-2 addition                                     | Outbus<br>Y           |

|----------------|----------------------------------------------------|-----------------------|

| 8              | _                                                  |                       |

| 9              | _                                                  | _                     |

| 10             | _                                                  | _                     |

| 11             | _                                                  | _                     |

| 12             | $W_0(X_1+X_5)+(\emptyset)$                         | _                     |

| 13             | $W_1(X_2 + W_4) + (W_0(X_1 + X_5))$                |                       |

| 14             | $W_2X_3 + (W_1(X_2 + X_4) + X_0(X_1 + X_5))$       | <del>-</del>          |

| 15             | $W_0(X_4+X_8)+\varnothing$                         | <i>Y</i> <sub>5</sub> |

| 16             | $W_1(X_5 + X_7) + (W_0(X_4 + X_8))$                | _                     |

| 17             | $W_2X_6 + (W_1(X_5 + X_7) + W_0(X_0(X_4 + X_8))$   | _                     |

| 18             | $W_0(X_7+X_{11})+(\varnothing)$                    | <i>Y</i> <sub>8</sub> |

| 19             | $W_1(X_8 + X_{10}) + (W_0(X_7 + X_{11}))$          | _                     |

| 20             | $W_2X_9 + (W_1(X_8 + X_{10}) + W_0(X_7 + X_{11}))$ |                       |

| 21             | $W_0(X_{10} + X_{14}) + (\emptyset)$               | Y <sub>11</sub>       |

| 22             | $W_1(X_{11} + X_{13}) + (W_0(X_{10} + X_{14}))$    |                       |

working of the algorithm and the synchronization of the various components of our chip.

The hardware of each PE requires no control logic except for the signal "switch" which is used to copy part of the  $X_i$  values into the buffer FIFO-2 to aid in the addition of these values before they are multiplied by the weights. In the PE architecture shown in Fig. 5, the two sets of lines connecting FIFO-1 and FIFO-2 cross each other and this organization is possible for small mask sizes since current VLSI technologies support double metal layers commonly. But for very large mask sizes where the number of cross-overs increases considerably, the organization becomes unsuitable for VLSI implementation. This problem can be solved by modifying the PE architecture to include a third FIFO as given in Fig. 6. As the  $X_i$  values enter FIFO-1, they also get loaded into FIFO-2 and, once every third cycle, the values in FIFO-2 are copied with the parallel load capability into FIFO-3. This type of organization is suitable for masks of any size. Note that the size of FIFO-2 and FIFO-3 will be the same and equal to  $\lfloor m/2 \rfloor$  where m is the mask size. The size of FIFO-1 is m.

### 4.3. Systolic Version of the Proposed Architecture

The efficient implementation of an algorithm is VLSI depends on several factors like the use of cells that can be repeated in space, extensive use of pipelining and

TABLE 3a

Trace of Clock-Step Execution of PE3 for the architecture of Fig. 3

| Clock | Inbus                 |                        | F                      | FO-1                   |                        |                        | FIF                   | 0-2                    |                        | Start                     |

|-------|-----------------------|------------------------|------------------------|------------------------|------------------------|------------------------|-----------------------|------------------------|------------------------|---------------------------|

| cycle | X                     | 1                      | 2                      | 3                      | 4                      | 5                      | 6                     | 7                      | CLA-1                  | multiply                  |

| 1     | <i>X</i> <sub>1</sub> | <i>X</i> <sub>1</sub>  | Ø                      | Ø                      | Ø                      | ø                      | ø                     | Ø                      | _                      |                           |

| 2     | X <sub>2</sub>        | <i>X</i> <sub>2</sub>  | <i>X</i> <sub>1</sub>  | ø                      | ø                      | Ø                      | ø                     | ø                      | _                      |                           |

| 3     | <i>X</i> <sub>3</sub> | <i>X</i> <sub>3</sub>  | <i>X</i> <sub>2</sub>  | <i>X</i> <sub>1</sub>  | ø                      | ø                      | Ø                     | Ø                      | _                      |                           |

| 4     | X <sub>4</sub>        | X <sub>4</sub>         | <i>X</i> <sub>3</sub>  | X <sub>2</sub>         | <i>X</i> <sub>1</sub>  | Ø                      | ø                     | Ø                      | _                      |                           |

| 5     | X <sub>5</sub>        | <i>X</i> <sub>5</sub>  | X4                     | <i>X</i> <sub>3</sub>  | <i>X</i> <sub>2</sub>  | <i>X</i> <sub>1</sub>  | ø                     | Ø                      | _                      | <del>-</del>              |

| 6     | X <sub>6</sub>        | <i>X</i> <sub>6</sub>  | <i>X</i> <sub>5</sub>  | X <sub>4</sub>         | $X_3$                  | X <sub>2</sub>         | <i>X</i> <sub>5</sub> | X <sub>6</sub>         |                        |                           |

| 7     | X <sub>7</sub>        | <i>X</i> <sub>7</sub>  | <i>X</i> <sub>6</sub>  | <i>X</i> <sub>5</sub>  | <i>X</i> <sub>4</sub>  | X <sub>3</sub>         | ø                     | X <sub>5</sub>         | $X_2 + X_6$            |                           |

| 8     | <i>X</i> <sub>8</sub> | X <sub>8</sub>         | X <sub>7</sub>         | <i>X</i> <sub>6</sub>  | X <sub>5</sub>         | X <sub>4</sub>         | ø                     | ø                      | $X_3 + X_5$            | $W_0(X_2+X_6)$            |

| 9     | Х,                    | X <sub>9</sub>         | X <sub>8</sub>         | <i>X</i> <sub>7</sub>  | <i>X</i> <sub>6</sub>  | X <sub>5</sub>         | X <sub>8</sub>        | <i>X</i> <sub>9</sub>  | X <sub>4</sub> + Ø     | $W_1(X_3+X_5)$            |

| 10    | X <sub>10</sub>       | X <sub>10</sub>        | Х,                     | <i>X</i> <sub>8</sub>  | Χ <sub>γ</sub>         | X <sub>6</sub>         | ø                     | <i>X</i> <sub>8</sub>  | $X_5 + X_9$            | $W_2(X_4)$                |

| 11    | X <sub>11</sub>       | <i>X</i> <sub>11</sub> | <i>X</i> <sub>10</sub> | <i>X</i> <sub>9</sub>  | <i>X</i> <sub>8</sub>  | <i>X</i> <sub>7</sub>  | Ø                     | ø                      | $X_6 + X_8$            | $W_0(X_5+X_9)$            |

| 12    | X <sub>12</sub>       | X <sub>12</sub>        | X <sub>11</sub>        | X <sub>10</sub>        | <i>X</i> <sub>9</sub>  | X <sub>8</sub>         | X <sub>11</sub>       | X <sub>12</sub>        | $X_7 + \emptyset$      | $\overline{W_1(X_6+X_8)}$ |

| 13    | X <sub>13</sub>       | X <sub>13</sub>        | X <sub>12</sub>        | <i>X</i> <sub>11</sub> | X <sub>10</sub>        | <i>X</i> <sub>9</sub>  | Ø                     | <i>X</i> <sub>11</sub> | $X_8 + X_{12}$         | $W_2(X_7)$                |

| 14    | X <sub>14</sub>       | X <sub>14</sub>        | X <sub>13</sub>        | <i>X</i> <sub>12</sub> | <i>X</i> <sub>11</sub> | X <sub>10</sub>        | ø                     | Ø                      | $X_9 + X_{11}$         | $W_0(X_8+X_{12})$         |

| 15    | X <sub>15</sub>       | X <sub>15</sub>        | X <sub>14</sub>        | X <sub>13</sub>        | <i>X</i> <sub>12</sub> | <i>X</i> <sub>11</sub> | X <sub>14</sub>       | X <sub>15</sub>        | $X_{10} + \varnothing$ | $W_1(X_9 + X_{11})$       |

parallelism, and avoidance of global communication. The chip proposed in Section 4.1 uses a PE cell that can be repeated in space and the algorithm has a high degree of pipelining and parallelism. But the algorithm requires global broadcast of the input to all the PEs in parallel and, similarly, the output from any PE has to be connected to the output pads through a common bus. This can be achieved without degradation of performance by using powerful bus drivers and precharge logic. However, a better alternative is to use a systolic algorithm where global communication is avoided. We will show that our algorithm can be modified such that is can be implemented using a systolic array without changing the PE architecture.

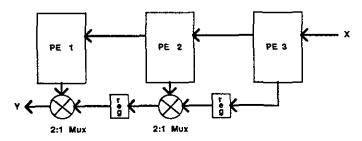

The systolic organization of the PEs is shown in Fig. 7. The basic PE architecture remains the same and the figure depicts the organization for the example discussed in the previous section where a mask of size 5 is assumed. The bus that connected the outputs of all the PEs in Fig. 3 is replaced by a set of multiplexers and registers as shown in Fig. 7. This modification is necessary since in the new algorithm, all the PEs output their results simultaneously during the same clock cycle. During this cycle, the 2:1 multiplexers select the  $Y_i$  values from the PEs to be loaded into the corresponding registers. During the rest of the cycles, the results stored in the registers are shifted left to be output sequentially. When the results are being shifted out, the PEs continue to compute the next set of  $Y_i$  values. Our algorithm works

TABLE 3b

| Clock<br>cycle | CLA-2 addition                                        | Outbus<br>Y           |

|----------------|-------------------------------------------------------|-----------------------|

| 8              | -                                                     | _                     |

| 9              | <u> </u>                                              |                       |

| 1Ö             |                                                       | <del>-</del>          |

| 11             | <del>-</del>                                          | _                     |

| 12             | _                                                     | _                     |

| 13             | $W_0(X_2+X_6)+(\emptyset)$                            | _                     |

| 14             | $W_1(X_3 + X_5) + (W_0(X_2 + X_6))$                   |                       |

| 15             | $W_2X_4 + (W_1(X_3 + X_5) + W_0(X_2 + X_6))$          | _                     |

| 16             | $W_0(X_5+X_9)+(\emptyset)$                            | <i>Y</i> <sub>6</sub> |

| 17             | $W_1(X_6+X_8)+(W_0(X_5+X_9))$                         | _                     |

| 18             | $W_2X_7 + (W_1(X_6 + X_8) + W_0(X_5 + X_9))$          | _                     |

| 19             | $W_0(X_8+X_{12})+(\varnothing)$                       | <i>Y</i> <sub>9</sub> |

| 20             | $W_1(X_9 + X_{11}) + (W_0(X_8 + X_{12}))$             |                       |

| 21             | $W_2X_{10} + (W_1(X_9 + X_{11}) + W_0(X_8 + X_{12}))$ |                       |

| 22             | $W_0(X_{11} + X_{11}) + (\emptyset)$                  | Y <sub>12</sub>       |

such that when all the results have been output, the PEs are ready to output a new set of results. Thus, the chip outputs a resultant pixel value  $Y_i$  at the rate of one per cycle.

The algorithm works as follows: a new pixel value  $X_i$  is input to the right most processing element PE3 during each clock cycle. In the following cycle, the PE3 will pass on the value to the neighboring PE2 while it receives a new one. This can be done by connecting the output of the first register in FIFO-1 to the input of the neighboring PE. Tables 4-6 illustrate the working of the algorithm as well as the synchronization of the PEs. Since the signal "switch" within each PE has to be "on" at the same time and at regular intervals, the signal can be controlled globally. Always, this signal is high only during the cycle that precedes the one when the PEs produce a new set of results. Hence the same signal can be delayed by one cycle to control the multiplexer at the corresponding stage. The multiplexer forwards the result from the neighboring PE during each clock cycle, except when new results are generated. Then the result from the PE in the corresponding stage is forwarded.

#### 4.4. Normalization

The convolved image consists of 16-bit values which are output by the PEs. If the system is built to obtain a Gaussian filter, then the resultant image pixels have to be normalized to 8-bit values in order to display the filtered image. Since the original

Fig. 6. A modified architecture for the processing element.

Fig. 7. A systolic version of the proposed chip. This is an alternate proposal to that of Fig. 3.

pixels are 8-bit values, the resultant pixel values after the Gaussian convolution can be divided by 256 to yield values less than 255. This can be achieved by performing arithmetic shift-right eight times, which is equivalent to dividing by 2<sup>8</sup>. However, by doing this we will lose some accuracy if the value being shifted is negative. To avoid this, we will use an alternate method which is to take the 8 most significant bits and add the sign bit to it. Thus, the normalization requires an 8-bit adder circuit and can be performed in one clock cycle.

# 4.5. Zero-Crossing Detector